## Ku-Band Low Noise Amplifier with Using Short-Stub ESD Protection

Chang-Kun Park, Min-Gun Kim\*, Chung-Han Kim\*, and Songcheol Hong

Dept. EECS, Korea Advanced Institute of Science and Technology (KAIST)

373-1, Guseong-dong, Yuseong-gu, Daejeon, 305-701, Republic of Korea

\*Teltron, 202 ITplex, 59-2, Jang-dong, Yuseong-gu Daejeon, 305-343, Republic of Korea

**Abstract** — A Ku-band ESD-protected low noise amplifier is designed using 0.15um pHEMT process. The input ESD protection is implemented with short-circuited stub. Since a short-circuited stub is used as an ESD protection as well as a matching element, there are no additional components and parasitic components associated with ESD protection. This endures 4400V (ESD tester limit) HBM test signal. The LNA has the noise figure of 1.24 dB and 24.5 dB gain at the frequency of 11.7-12.75 GHz.

### I. INTRODUCTION

The ESD protection method for RF integrated circuits becomes more important as operation frequencies increase. The parasitic capacitances of ESD protection elements make it very difficult to design high frequency circuits. Although some ESD protection methods were proposed, such as distributed ESD protection [1][4], there are few works on ESD protection issues for high frequency applications. Also, the ESD protection issues in compound semiconductor microwave monolithic integrated circuits have not been discussed seriously yet [2]. Because thermal conductivities of compound semiconductors are much lower than silicon, compound semiconductor MMICs are more sensitive to ESD events [2]. Especially, inputs of LNAs are vulnerable to ESD events. Here, we proposed a solution to protect high frequency MMICs from ESDs. The Ku band LNA is addressed, which endures 4400V(tester limit) HBM test.

### II. ESD PROTECTION USING SHORT-CIRCUITED STUB

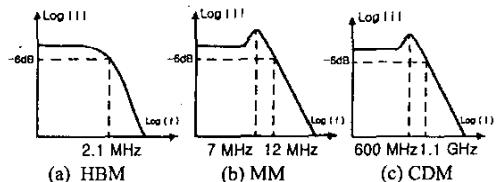

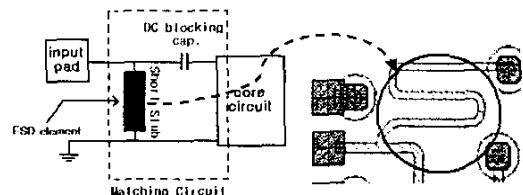

Fig.1 shows power distributions of current waveforms in various ESD tests such as HBM, MM and CDM. All of them have much lower bandwidth compare to microwave region at which most of MMICs work. Using the frequency characteristics of ESD signals, we designed the input matching circuit of Ku-band LNA with a high pass filter, which consists of a short stub placed at the very front as in Fig. 2. RF signal flow from the input port to the amplifier circuit. When ESD event is occurred, the ESD current

shunt to ground through the short stub between input pad and ground.

Fig. 1. Frequency spectrum of the current waveform calculated for (a) human body model (HBM), (b) machine model (MM), (c) charged device model (CDM). After [3]

Fig. 2. Short-circuited stub as ESD element

During ESD events, the circuits must not be destroyed. Capacitors or resistors whose ESD capability is very low [5] must not be located in the ESD current path. This is the very reason why we designed the short-circuited stub to be situated in front of DC blocking capacitor. ESD protection device can endure high ESD voltages by minimize power dissipation during the events. It is well known that the thermal conductivities of compound semiconductors are lower than that of Silicon. Thus, MMIC based on compound semiconductor is more sensitive to ESD. Parasitic components of ESD protection device make it very difficult to design matching networks at high frequencies. Because compound semiconductors are more vulnerable to ESD, the conventional ESD device tends to be more bulky than silicon based one. In addition, since compound semiconductors are used in high frequency

applications, the parasitic elements cause serious troubles. The proposed ESD protection method using short-circuited stub can be a solution in high frequency ICs. Because the protection element of short-circuited stub is composed of only metal lines, the power dissipation of the protection device during ESD event is very small. This is the reason why the ESD device can endure very high ESD voltage.

### III. RF CHARACTERISTICS OF THE LNA

2 stage LNA is designed and fabricated with 0.15um pHEMT. The RF characteristics of designed LNA are showed in Table 1.

TABLE I

SUMMARY OF SIMULATION AND TEST RESULTS

|                            | simulation       | Test Results     |

|----------------------------|------------------|------------------|

| <b>Operation Frequency</b> | 11.7 ~ 12.75 GHz | 11.7 ~ 12.75 GHz |

| <b>Noise Figure</b>        | < 1.08 dB        | < 1.24 dB        |

| <b>Gain</b>                | 24.5 dB          | ~ 24.5 dB        |

| <b>P1 dB</b>               | No results       | 5.67 dBm         |

| <b>S11 &amp; S22</b>       | < -22 dB         | < -16 dB         |

| <b>Vd, Vg</b>              | 2V, -0.6V        | 2V, -0.6V        |

| <b>Total Current</b>       | 48 mA            | 48 mA            |

| <b>Temperature</b>         | 25 °C            | 25 °C            |

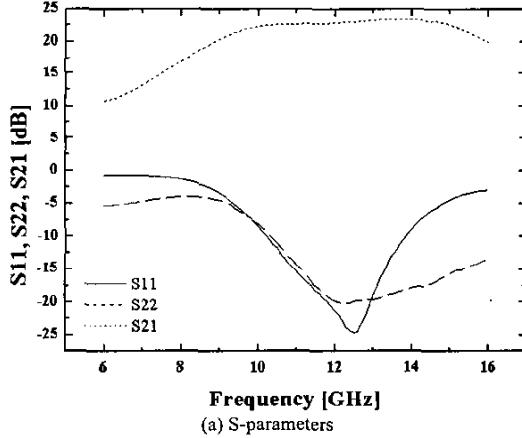

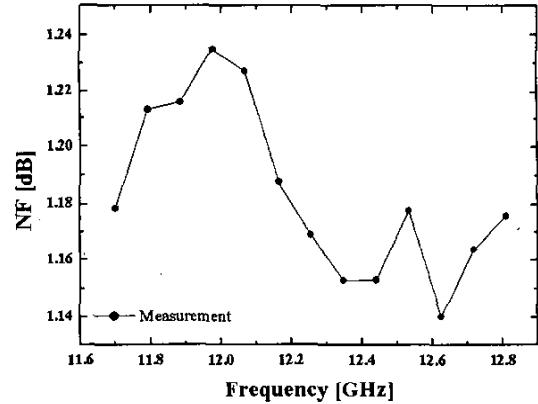

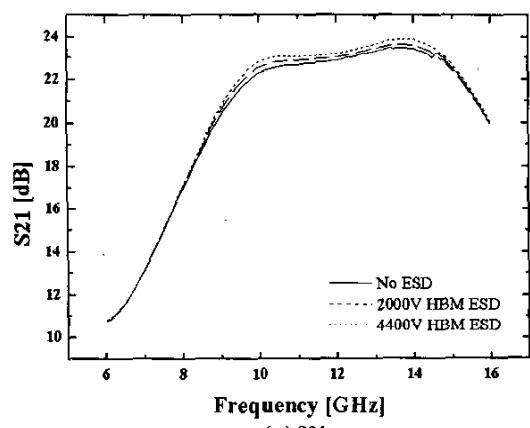

Since ESD events occur frequently in the input of LNA, the protection device place only in input part. The same method can be applied to the output. Here, no ESD protections are applied to the output to compare ESD endurances. Figure 3 shows the measured s-parameters and noise figure of designed LNA.

(a) S-parameters

(b) Noise Figure

Fig. 3. Test results of designed LNA

To get flat characteristics of gain, the feedback with capacitor and resistor between the drain of the first stage and the drain of the second stage is applied. The inductive degeneration in the first stage and common source topology allow low noise figure as well as high gain.

### IV. ESD TEST RESULTS

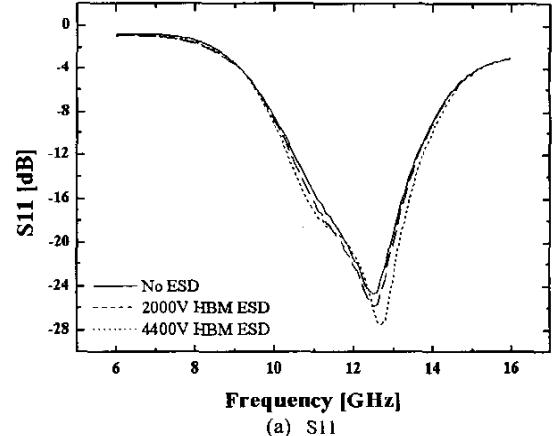

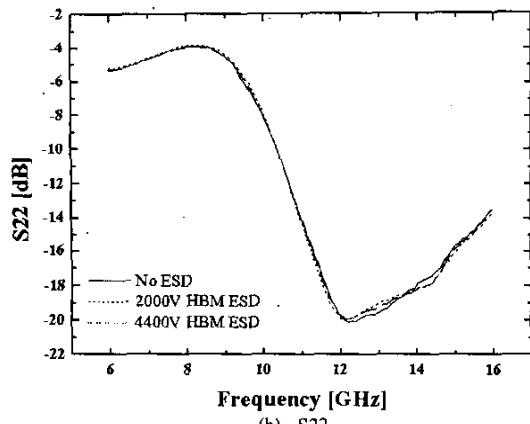

To test the proposed ESD protection using short-circuited stub, we measured the S-parameters of LNA after HBM ESD currents are applied to the input. We used the tester whose ESD voltage limit is ~ 4400V. We could not find any changes in the stub after the ESD test. No changes are measured in S-parameters, too. It implies that the protection device endures 4400V (tester limit) HBM ESD.

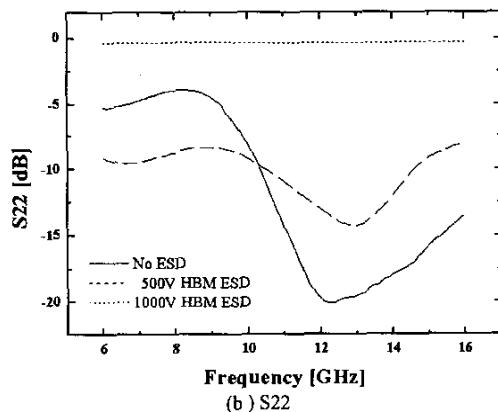

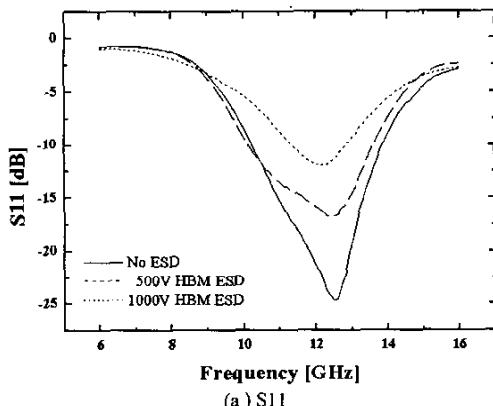

(a) S11

Fig. 4. Measured S-parameter after ESD test at input pad

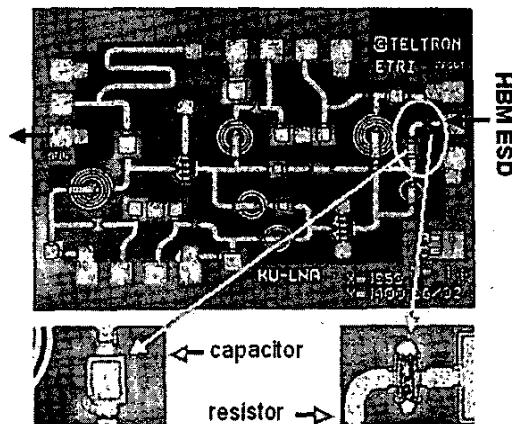

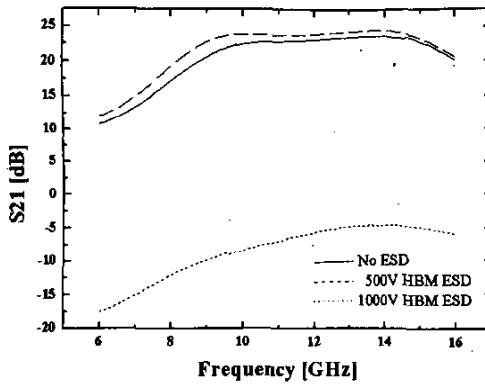

The HBM ESD tests in the output are performed and the also followed by S-parameter measurements. As is showed in the measured S-parameters (figure 6), the unprotected output part is very sensitive to the HBM ESD. First, the DC blocking capacitor of output part is destroyed at the lowest HBM ESD voltage, and the S-parameter is changed. In the figure 6, the dashed lines of S-parameters are measured after the failure of DC blocking capacitor. The dotted lines of S-parameters are measured after the failure of resistor. Although resistors are known to be more endurable to ESD than capacitors, the resistor was destroyed at the ESD voltage as low as 1000V. The pictures of the destroyed resistor and capacitor are showed in Figure 5.

Fig. 5. Picture of MMIC and the destroyed components after ESD test at output.

Fig. 6. Measured S-parameter after ESD test at output pad

While conventional ESD protection devices have substantial parasitic capacitances, the proposed ESD protection utilizes one part of matching circuits as a ESD protection device. Therefore, this protection method must be very efficient and effective at high frequency MMICs.

## V. CONCLUSIONS

An ESD protection using short-circuited stub is demonstrated, which is used as a part of matching circuits.

Ku band LNA with the protection device in the input was fabricated. This endures HBM ESD voltage as high as 4400V (tester limit). This method becomes more efficient as the operating frequency increases. The LNA shows the noise figure of 1.24 dB and 24.5 dB gain at the frequency range of 11.7-12.7 GHz.

## ACKNOWLEDGEMENT

This work was supported by KOSEF under the ERC program through the MINT research center at Dongguk University.

## REFERENCES

- [1] B. Kleveland, et al., "Distributed ESD Protection for High-Speed Integrated Circuits" *IEEE Electron Device Lett.*, vol. 21, no. 8, pp. 390-329, 2000

- [2] K. Bock., "ESD issues in compound semiconductor high-frequency devices and circuits" *Microelectronics Reliability*, vol. 38, pp. 1781-1793, 1998.

- [3] Ajith Amerasekera, Charvaka Duvvury, "ESD in silicon integrated circuits" *WILEY*, pp. 17-19, 1996.

- [4] B. Kleveland and T. H. Lee, "Distributed ESD protection device for high speed integrated circuits", U. S. Patent 5,969,929.

- [5] G. Croft, J. Bernier, "ESD protection techniques for high frequency integrated circuits" *Microelectronics Reliability*, vol. 38, pp. 1681-1689, 1998.